# Semiconductor Manufacturing and Advanced Research with Twins Manufacturing USA Institute SMART USA

**Emily Dean**Operation Manager

SMART USA Institute

10/22/2025

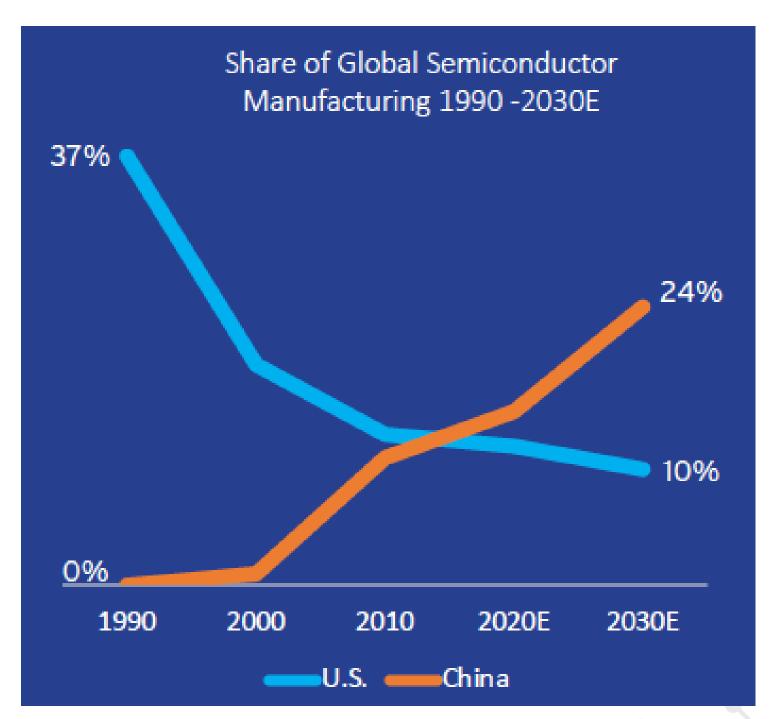

# Why is the CHIPS Act needed?

- Supply Chain Resilience

- Economic Security

- National Security

https://www.semiconductors.org/turning-the-tide-for-semiconductor-manufacturing-in-the-u-s/

# **CHIPS Manufacturing USA**

Mission: Collaboratively address challenges faced with manufacturing focused digital twins

Significantly produ

Reduce Cost of U.S. Chip

development

Improve

Development

Cycle-Times of

Semiconductor

Product

Innovation

and

Manufacturing

https://www.nist.gov/system/files/documents/2024/05/17/CHIPS\_MfgUSA\_Proposers%20Day\_NOFO\_05152024-508C.pdf

Convene

Stakeholders

across the

Semiconductor

production

Ecosystem

NOFO

Defined

Objectives

Advance Digital

twin enabled

criteria for

training a

domestic

workforce

Improve the state-of-the-art in Manufacturing relevant digital twins

twin

Marketplace for industry access to digital twins

# SMART USA's four defined objectives to be achieved in a five-year period.

- 1. 40% reduction in development and manufacturing costs

- 2. 35% reduction in process development cycle time

- 3. 40% increase in yield

- 4. Train and educate > 110K workers for the industry

# **Operational Areas**

- Projects will all fall within one of the following Operational Areas, (OA).

- Project focal topics change every solicitation, but all aim to move the marker closer to achieving our institute level targets.

**Institute Operations**

- Build the Ecosystem

- Build Governance and Management plans

- Institute sustainability

OA2

Shared Physical and Computational Capabilities

- SMART Backbone

- Digital SMART Marketplace

**OA3**

**Industry-Led Solutions**

- Improve Digital twin diversification

- Establish quantification method for evaluating digital solutions

**OA4**

### Education & Workforce Development

- Digital Innovation

Semiconductor Centers (DISCs)

- Digitally Trained Workforce platform

### Digital Twins Approach

What are they? | Why do they matter?

A virtual representation or model serving as a real-time digital counterpart of a physical object or process

- Innovate faster and at less expense

- Shorten process design and validation times

- Improve manufacturing performance

- Enhance training

### Challenges

### **Fragmentation**

Inability to access data needed to validate digital twins and power machine learning and Al tools

### **Lack of Trust**

Unwilling to take risk to work across organization boundaries

### **High Barriers to Entry**

Significant investment to participate, which is out of reach for SME manufacturers

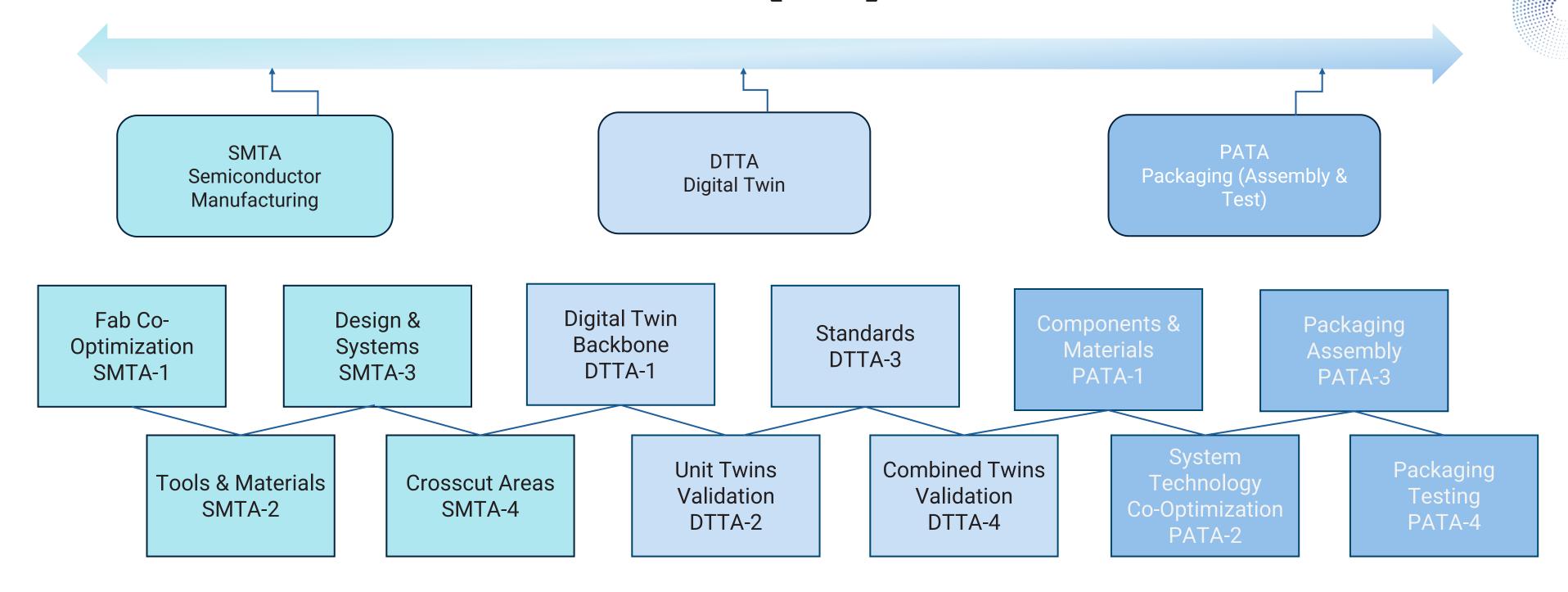

# Technical Thrust Areas (TA)

### **WORKFORCE DEVELOPMENT**

### SMART USA Infrastructure

The U.S. is facing a tremendous semiconductor workforce shortage of 67,000 semiconductor workers by 2030.

SMART USA aims to use digital twins to help fill gap at speed and at scale.

Our programs will target:

- Digital twin engineers

- U.S. semiconductor workers

Key partnerships will bring digital twins to classrooms and virtual learning environments across the country, making careers in semiconductors accessible like never before.

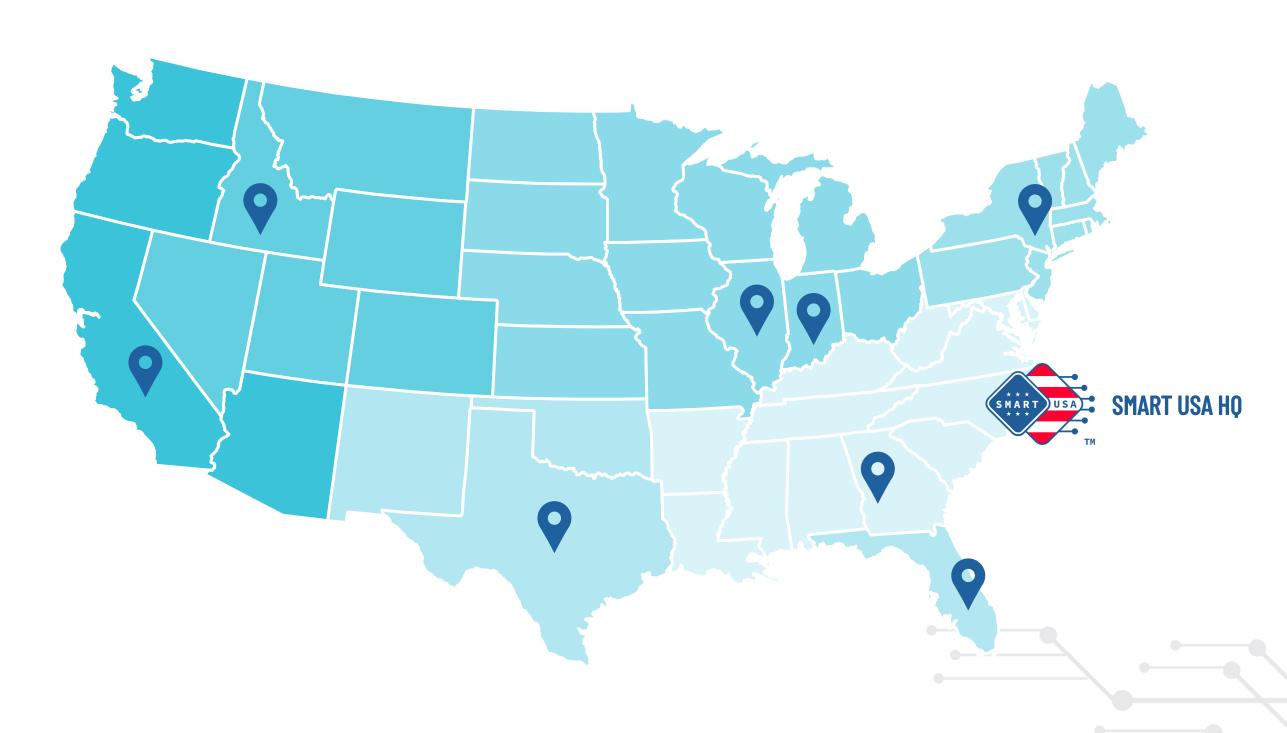

# DISC Network

### SMART USA Infrastructure

Digital Innovation

Semiconductor Centers,

DISCs, bring SMART USA to

communities across the

country.

### Achievement looks like:

- Training Programs

- Accessibility

- Connection

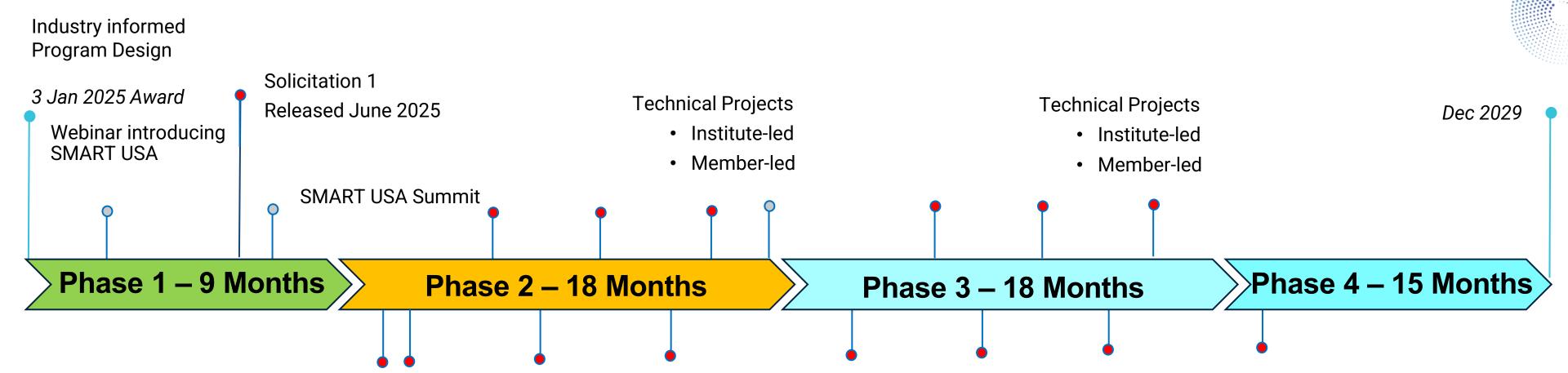

### **SMART USA - Plans, Accomplishments**

Solicitation 2 release October 2025 Solicitation 3 release December 2025

### Phase 2 objectives

- Physical and Computational Capabilities

- shared facilities network

- digital twin backbone.

- Digital Twin Standards

- Digital Marketplace Launched and Validated

- Workforce Platform Launched and Validated

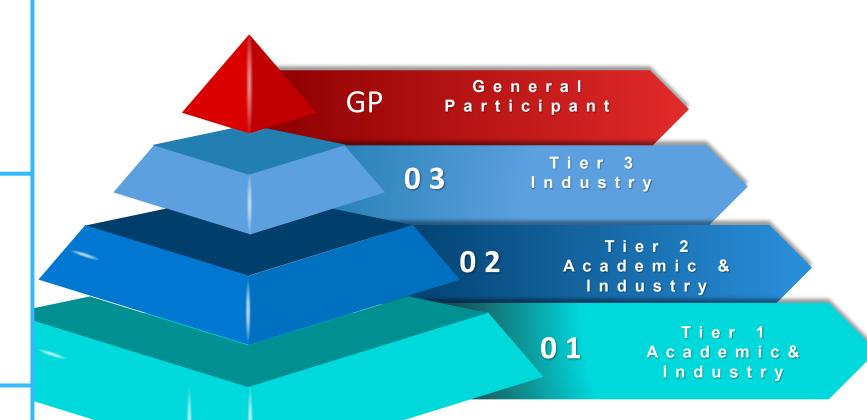

# **Project Types**

- Institute-Led Collaborative Projects Carried out by institute staff or subcontractors, intended to accelerate objectives of the institute, or provide greater access and advancements to the membership ecosystem.

- **Member-led Collaborative** Often led by university teams and required to maintain collaboration with a minimum of three different industry partners. These projects are expected to yield innovations and IP owned by the project performing members, this technology is anticipated to have commercial impact and help the industry progress to meet institute objectives.

- Member-Led Proprietary Led by either industry or academia with surplus membership funds, not spent on collaborative proposals. These projects are executed via a team, and may be a novel topic, or a continuation of a previous project. IP rights are dictated at the time of proposal submission.

## MEMBERSHIP OPTIONS

### **Industry**

SMART USA welcomes businesses of all sizes to participate.

Opportunities include rights to IP, access to funding calls, and collaboration.

15X Return

### **Academia**

SMART USA seeks engagement from research and academic institutions with opportunities to participate in funding calls and collaboration.

15x Return

10/22/20

# Learn about becoming a member

# Reach out to us regarding Membership!

https://www.smartusatwins.org/membership/join/

MAPT Roadmap

# MAPT Road Map Version 2

The industry's first 3D semiconductor roadmap

- Now contains Chapter 12 on Digital Twins

- 370 Experts across 132 organizations helped author.

- Translates the 2030 decadal plan

- Seismic shifts into actionable strategies for Chipmaking.

# **Proud Member of Manufacturing USA**